Review of The Simulation and Evaluation of Dynamic Voltage Scaling Algorithms by Trevor Pering, Tom Burd, and Robert Brodersen

Abstract

The energy consumption reduction in microprocessors can be achieved by Dynamic Voltage Scaling (DVS). The algorithm is based on certain benchmarks. The DVS algorithm is implemented by a software control and the voltage is varied dynamically based on the performance requirements.

Motivation

The PDA class devices have functions like User Interface (UI), audio and mpeg playback. These devices use general processors and the processor has relatively high idle times. Trevor Pering, Tom Burd, and Robert Brodersen have simulated and evaluated DVS algorithm that reduces the energy consumption of these devices based on the benchmark.

Observation

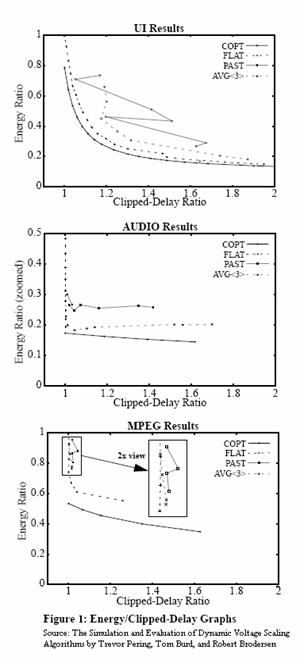

By decreasing the supply voltage we can reduce the energy consumption, but the offset of this that we increase the delay. By DVS we give minimum clock frequency necessary without much latency. They have used 3 benchmarks to analyze the algorithms. User-Interface, Audio and MPEG are the benchmarks. Four algorithms are used to study these benchmarks - FLAT, COPT, PAST and AVG<weight>.

FLAT algorithm is without voltage scaling. The operating voltage is at a fixed level. This algorithm is used to calculate the power consumption with a fixed voltage.

Clipped Optimal (COPT) algorithm is a theoretical algorithm and is used to compare with realizable algorithms. The COPT algorithm calculates the minimum energy of a system for a given delay.

PAST algorithm is a realizable algorithm. The algorithm calculates the previous interval and dynamically changes the voltage and frequency. The limit of this algorithm is that it cannot be used on a system that is almost busy or idle for the present process to calculate delay for the next process.

AVG<weight> calculates the next average by taking into account the previous running average. The limit of this algorithm is that the results are dependent on the weight parameter.

The three benchmarks or events have different delay patterns. The UI event delays are dependent on the user and usually have short bursts of busy time. The audio events have even delays as the input data rate is constant and the processor job is to output data to external device. The MPEG decoding is done using inverse discrete cosine transform (IDCT). The processing time varies depending on the number of ICDTs. The frame period is fixed at 71ms.